Trusted Platform Module (TPM) версии 1.2 против 2.0 и количество выводов в заголовке

Я пытаюсь понять заголовок TPM на моей материнской плате, которая является Asrock "H170m Pro4" TPMS1 заголовок на материнской плате, и он имеет 9x2 контактов с 1 отсутствует.

При поиске в Интернете я вижу 14-1-контактный модуль TPM, другие ссылки на 20-контактные. в чем дело?

Вот ссылка на сайт производителя для конкретного mobo, для которого я пытаюсь получить чип TPM. Вы можете скачать руководство здесь: https://www.asrock.com/mb/Intel/H170M%20Pro4/

в H170M Pro4.pdf на страницах 6 и 7 показано TPMS1 расположение заголовка и на странице 22 он сообщает 17-контактный TPMS1 и что делает каждый контакт

- PCICLK нижний ряд слева больше всего

- Рамка нижнего ряда направо

- PCIRST #

- LAD3

- + 3v

- LAD0

- нет булавки

- + 3VSB

- GND нижний ряд справа самый

- GND верхний ряд слева больше всего

- SMB_CLK_MAIN

- SMB_DATA_MAIN

- LAD2

- LAD1

- GND

- S_WRDWN # это выше пустого контакта # 7

- SERIRQ

- GND верхний ряд справа наиболее

меня беспокоит и беспокоит использование TPMS1 и вот на их сайте https://www.asrock.com/mb/spec/card.asp?Model=TPM-S%20Module ссылкой на эти 3 вещи:

- Модуль TPM-S (V 1.2)

- Модуль TPM-s (V 2.0)

- Модуль TPM2-S (V 2.0)

Кто-нибудь может понять это?

2 ответа

TL;DR: Это куча мусора, и на нее нет хорошего ответа.

Поскольку хорошего ответа нет , я хотя бы рассмотрю некоторые нюансы вопроса: в чем дело ?

Приношу извинения, так как это не ответ на вопрос (я полагаю), который вы задумали (т. е. на основе обещаний TPM... то есть покупка устройства, которое я хочу, от производителя, которого я предпочитаю, исходя из его позиции безопасности и реализованных функций. какова распиновка материнской платы, чтобы я мог подключить к плате нужный TPM).

Увы, я могу ответить на этот вопрос, но (как уже упоминалось) это гораздо больше поможет охватить мета-проблему: «В чем дело?»

История доверенного платформенного модуля

Чтобы донести до будущих читателей, о чем вообще этот пост, давайте рассмотрим основы:

Прежде всего, Trusted Platform Module (также известный как TPM) — это реализация спецификации, созданной и поддерживаемой Trusted Computing Group.

Цель TPM — действовать как вторичное вычислительное устройство для выполнения определенных операций полностью независимо от основного процессора. Связь между основным процессором и TPM обычно осуществляется через интерфейс с малым числом контактов (LPC) или (в последнее время) последовательный периферийный интерфейс ¹ (SPI).

Существует две основные версии спецификации: 1.2 и 2.0. Спецификация 2.0 была (более или менее переписанной с нуля²).

В спецификации 2.0 есть четыре определенные области:

- Архитектура:

Часть 1 TPM2.0 содержит подробное описание свойств, функций и методов TPM. Если не указано иное, данное повествовательное описание является информативным. Часть 1 TPM2.0 содержит описания некоторых процедур манипулирования данными, которые используются в этой спецификации. Нормативное поведение этих подпрограмм записано в коде C в TPM2.0, часть 3 и TPM2.0, часть 4. Алгоритмы и процессы, описанные в этом TPM2.0, часть 1, можно сделать нормативными посредством ссылки из TPM2.0, часть 2, TPM2.0, часть 3 или TPM. 2.0 Часть 4.2. Конструкции -

Часть 2 TPM2.0 содержит нормативное описание констант, типов данных, структур и объединений для интерфейса TPM. Если не указано иное: (1) все таблицы и код C в TPM2.0, часть 2, являются нормативными, и (2) нормативное содержание в TPM2.0, часть 2 имеет приоритет над любой другой частью данной спецификации.

- Команды -

Часть 3TPM2.0 содержит: (1) нормативное описание команд, (2) таблицы, описывающие форматы команд и ответов, и (3) код C, иллюстрирующий действия, выполняемые TPM. В TPM2.0, часть 3, таблицы команд и ответов имеют наивысший приоритет, за ними следует код C, за которым следует описательное описание команды. TPM2.0, часть 3, подчиняется TPM2.0, часть 2. TPM не обязательно реализовывать с использованием кода C в TPM2.0, часть 3. Однако любая реализация должна обеспечивать эквивалентные или, в большинстве случаев, идентичные результаты, наблюдаемые на интерфейсе TPM или продемонстрировано посредством оценки. 4. Поддерживающие процедуры –

В TPM2.0, часть 4, представлен код C, который описывает алгоритмы и методы, используемые командным кодом в TPM2.0, часть 3. Код в TPM2.0, часть 4, дополняет части 2 и 3, предоставляя полное описание TPM, включая вспомогательную структуру для код, выполняющий действия команды. Любой код TPM2.0, часть 4, может быть заменен кодом, который обеспечивает аналогичные результаты при взаимодействии с кодом действия в TPM2.0, часть 3. Поведение кода TPM2.0, часть 4, не включенного в приложение, является нормативным, как это наблюдается на интерфейсах с TPM. 2.0 Код части 3. Код в приложении предоставлен для полноты, то есть для обеспечения полной реализации спецификации.

Мысленно я предпочитаю сопоставлять их с четырьмя основными аспектами функционирования TPM³:

Программное обеспечение, работающее на основном процессоре, которое будет использовать TPM (например, Bitlocker, OpenSwan и т. д.).

Платформа , которая желает использовать функциональные возможности, реализованные TPM ( обычно это интеллектуальная собственность , разработанная или лицензированная производителем). Часто это скорее интерфейс между основным процессором и самим TPM.

Интегральная схема , обеспечивающая встроенную систему, которая реализует необходимое аппаратное обеспечение для соответствия архитектуре TPM2.0, часть 1 (например, линейка систем на кристалле Optiga от Infineon или аналогичные устройства отST или Nuvoton.

Наконец-то прошивка работает на интегральной схеме. По состоянию на 2020 год это обычно «TSS» (стек программного обеспечения TPM2). Это может быть свободный/открытый исходный код (как в случае с эталонной реализацией TrouSerS , а также TPM2-TSS иTSS.MSR от Microsoft ) или проприетарные реализации.

Так в чем же дело?

::вздох:: В лучшем случае у нас останутся псевдостандарты. В устройствах TPM 1.2 многие поставщики реализовали 20-контактный (19 контактов с 1 шпонкой) или 14-контактный разъем (13 контактов с 1 шпонкой). Выбор того, как это реализовать, был оставлен на усмотрение поставщика «платформы» (например, MSI, Asus, SuperMicro и т. д.) и разработчика оборудования TPM (см. список выше).

Этот уровень выбора был сохранен при внедрении TPM2.0 с добавлением того, что по мере того, как безопасность платформ становится все более важной и появляется больше технологов с опытом (и мнениями) о том, как следует использовать TPM, растет количество вариантов . .

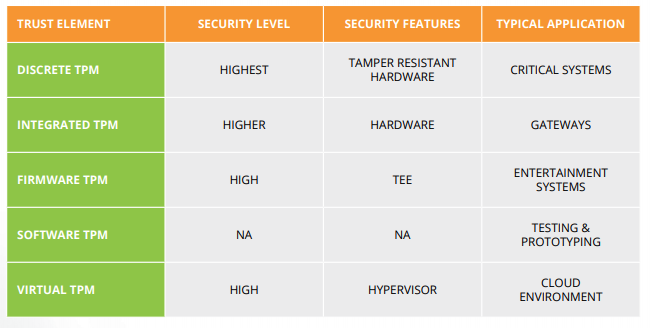

Давайте посмотрим на документ « TPM2.0: Краткое введение », опубликованный Trusted Computing Group. В этом документе автор призывает:

Таким образом, TPM может быть полностью интегрированным и необслуживаемым на месте, доступным через сменный контактный разъем или через 100% программное обеспечение.

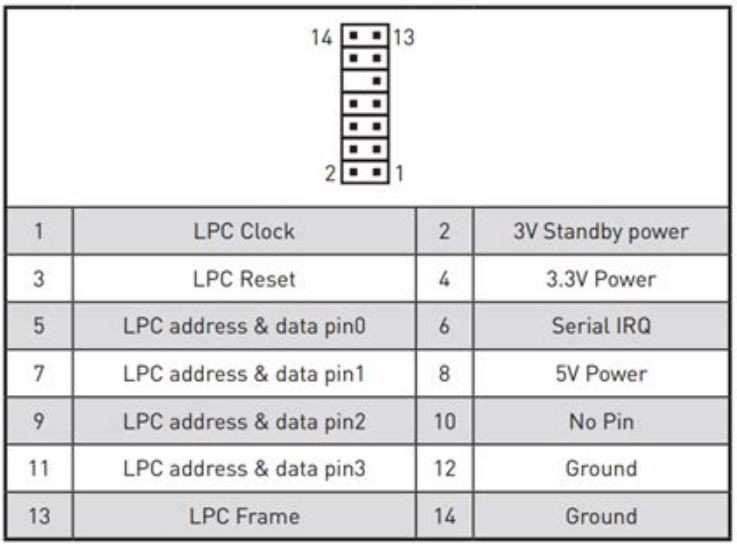

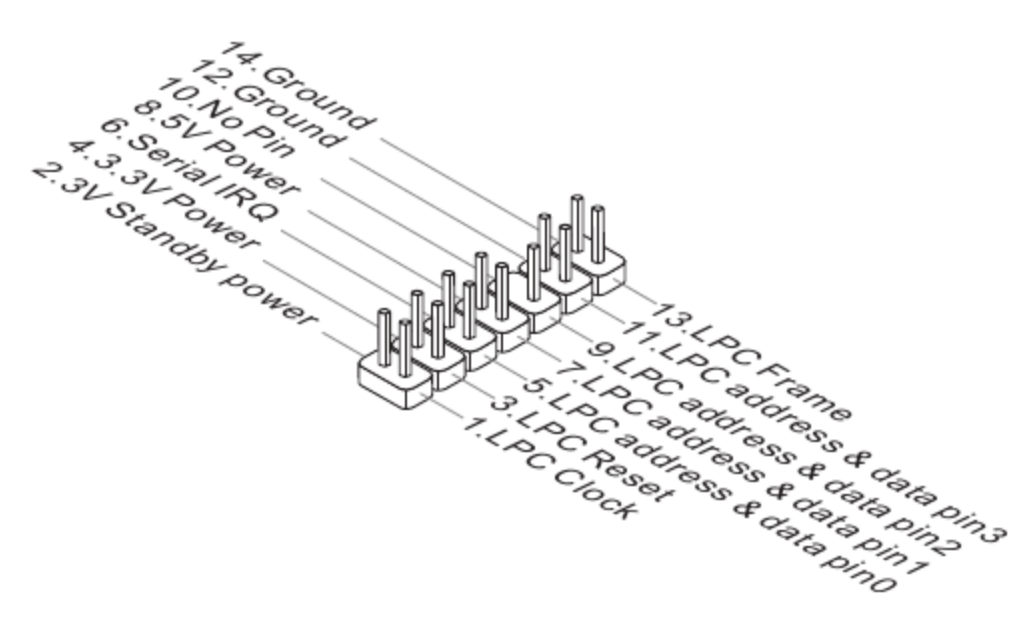

Что касается распиновки 14-контактного варианта, мне удалось найти несколько изображений с общими распиновками (поэтому я называю это псевдостандартом), например:

и

Конечно, опять же... причина, по которой я вообще здесь, - это попытка выяснить распиновку AOM-TPM-9670 от SuperMicro, которая основана на Infineon 9670... с 10-контактным разъемом.

Я ломал голову над реализацией 10-контактного разъема , пока не увидел это на странице 288 первой части спецификации реализации TPM2.0:

TPM может иметь один или несколько контактов ввода-вывода, которые вводят или выводят логическое состояние. TPM2_NV_Read и TPM2_NV_Write могут использоваться для доступа к значению GPIO с использованием обычных средств управления доступом. Спецификация для конкретной платформы определяет сопоставление индексов NV с отдельными вводами-выводами общего назначения (GPIO). Резервирует ли TPM какое-либо хранилище NV для указанного GPIO, зависит от платформы.

Это... насколько я понимаю, различное количество контактов (и в некоторых редких случаях расположение контактов) является функцией этого «выбора», предоставляемого разработчику платформы, позволяющего использовать такие вещи, как вторичные доказательства несанкционированного доступа или внеполосное взаимодействие с другими аппаратные устройства.

Примечания/Цитаты

¹: вариант SPI («расширенный последовательный периферийный интерфейс» или «eSPI») был разработан Intel как преемник LPC.

²: Из « Практического руководства по TPM2.0 » (Глава 1: История TPM):

Говорят, что лучшие проекты получаются, когда архитекторы создают проект, а затем, узнав все проблемы, с которыми они могут столкнуться, выбрасывают первый проект и начинают заново со второго. TPM2.0 дал архитекторам возможность сделать это. Однако им все равно нужно было убедиться, что возможности разработки программного обеспечения, которые открывались в TPM 1.2, не были потеряны с новой архитектурой.

Артур В., Челленер Д., Голдман К. (2015) История TPM. В: Практическое руководство по TPM2.0. Апресс, Беркли, Калифорния. https://doi.org/10.1007/978-1-4302-6584-9_1

³: Этот пример не работает в случае «виртуальных» TPM, подобных тем, которые реализованы QEMU, а также на некоторых мобильных телефонах и других встроенных устройствах. Для получения дополнительной информации о виртуальных TPM ознакомьтесь с документом 15-го симпозиума USENIX по безопасности: vTPM: Virtualizing the Trusted Platform Module .

Если ввести в поиск «модуль tpm», на AliExpress можно найти множество товаров. Обычно они имеют множество вариаций для разных поставщиков в зависимости от количества контактов. У них там есть 18-контактные TPM 2.0.